## Saudi Journal of Engineering and Technology

Abbreviated Key Title: Saudi J Eng Technol ISSN 2415-6272 (Print) |ISSN 2415-6264 (Online) Scholars Middle East Publishers, Dubai, United Arab Emirates Journal homepage: http://scholarsmepub.com/sjet/

**Review Article**

# **Porous Silicon Fabrication for MEMS Applications**

Ying Yue<sup>1\*</sup> and Nian Zhen<sup>2</sup>

<sup>1</sup>School of Material Science and Engineering, Wuhan University of Technology, 1040 Heping Ave, Wuchang, Wuhan, Hubei, China <sup>2</sup>School of Power Engineering, Wuhan University of Technology, 1040 Heping Ave, Wuchang, Wuhan, Hubei, China

**DOI:** 10.36348/SJEAT.2019.v04i10.003 | **Received:** 18.09.2019 | **Accepted:** 27.09.2019 | **Published:** 25.10.2019

\*Corresponding author: Ying Yue

#### **Abstract**

We describe the use of porous silicon fabrication technique for fabricating non-manhattan structures in silicon using wet etching. The fabrication method is simple to set up, economical and produces smooth etched surface. A solid source diffusion of N++ in a P type wafer with low stress thermally grown silicon nitride is used as a masking layer. Comparison of porous silicon etches with wafers solid source diffusion and implanted diffusion is presented. The result show that areas where a solid source diffusion is used form an etch angle of 70-80°, however using an implanted diffusion the etch angle is closer to 90°. The selectivity of the etch during porous silicon fabrication using any of the above two as masking layer results in fabrication of high aspect ratio non-manhattan structures. These structures since are wet etched do not have surface roughness and can be used for optical applications.

**Keywords:** Porous silicon, non-manhattan, high aspect ratio, MEMS, wet etching.

Copyright @ 2019: This is an open-access article distributed under the terms of the Creative Commons Attribution license which permits unrestricted use, distribution, and reproduction in any medium for non-commercial use (NonCommercial, or CC-BY-NC) provided the original author and source are credited.

#### INTRODUCTION

Successful implementation of the wet deep etching process would enhance the capabilities of state of the art MEMS processing by a) allowing fabrication of random geometries with high aspect ratio's using wet silicon etching b) drastically reducing the time required to fabricate high aspect ratio structures in silicon using the current state of the art c) reducing the cost of fabricating high aspect ratio structures by several orders of magnitude in comparison to the current state of the art, not to mention the advantage MEMS designers and fabrication experts will have in developing and manufacturing MEMS devices with the knowledge of the viability of such a technique [1-6]. Currently the technique that is employed to fabricate high aspect ratio structures in silicon is the DRIE. Although this technique has several advantages over conventional wet silicon etching, the costs of machinery and process materials are relatively high. Consequently the cost per wafer increases. The cost of a typical DRIE system with the ability to handle 4 inch wafers is expensive [7-9]. While the cost of processing the wafer using DRIE is based on features being etched and time, the typical cost of etching is economical. Wet etching of Si, commonly employed by the MEMS industry to fabricate membrane based structures and etches not requiring vertical sidewalls, is the preferred technique in the industry. The preference is based on simplicity, cost effective and easy implementation. While this is the

preferred etching technique, DRIE has found acceptance in the etching process because of the limitations of conventional wet etching, such as (a) the formation of a 54.7 degree sidewall angle while etching high aspect ratio structures in <100> type silicon, (b) very long etching times at elevated temperatures and (c) the limitation in achievable aspect ratio. Thus a need exists to develop and implement a wet etch technique that can produce high aspect ratio structures, like DRIE, employing a simple set up, that has minimal operating costs and, in a short period of time.

## **DEEP WET ETCHING (DWE)**

DWE is an alternative approach to DRIE and conventional wet etching. Our research exploited an alternate form of silicon etching namely the porous silicon etching technique, coupled with post processing techniques, to achieve high aspect ratio structures. The unique aspect of this research is the demonstrated process control that we can exercise on the etching process, to control the shape and morphology of mesopores of Si. While porous silicon etching has been an active area of contemporary research, most of the research efforts are focused on development of sensor applications [9, 10] or understanding the mechanisms of the process [5, 11-13]. The etched structures of this process are pores of Si of various diameters and shapes which can be modified by controlling various etch parameters and variables such as the applied voltage,

current density, etchant concentration, etch time, wafer type etc. Some attempts have been made in the past to create high aspect ratio through wafer structures by using the porous silicon technique through filling the pores with polysilicon, patterning and etching polysilicon and dissolving the pores [3, 8, 10, 12]. While achieving modest success, this techniques was still very time consuming and required numerous pre and post processing steps. Also, the walls of the resulting structures were scalloped due to the partially undissolved pores at the edge of the structures and the definition of the overall feature was compromised [4, 6, 10, 12].

DWE has its advantages of high aspect ratio in Silicon with side wall angles very close to 90 degrees, by controlled mesoporous Si etching. The principle of this technique is to effectively localize the pore formation phenomenon only in desired regions of the wafer. Our initial experiments confirm that it can achieved by masking the areas where etching is not desired with a mask and subjecting the wafer to porous silicon etching in a standard set up. This results in the unmasked area being etched with pores with average diameters of 40 nm. These pores are subsequently dissolved in a wet chemical etchant such as Tetra Methyl Ammonium Hydroxide (TMAH) or Potassium Hydroxide (KOH) at room temperature. The pore diameter effectively controls the roughness of the surface.

One of the primary challenges of this approach is to confine pore formation only to those areas of the wafer where etching is desired. We developed a combined optical/electrical pumping process with process control to control the region of nanopore growth. Another challenge is to maintain the vertical profile of the pores by optimizing the current density, applied voltage, etchant concentration [1, 2]. Pore branching can also compromise the definition of the desired structure, these issues are discussed in detail later. Although a nitride mask effectively stops pore formation, it is undercut there is considerable undercutting due to the presence of native oxide film prior to sputtering of the nitride film. The oxide film is attacked by the Hydrofluoric Acid solution and over the period of etching time erodes it away creating a liftoff of the nitride film. One possible way of overcoming this problem is to use epitaxially grown silicon nitride or chemical vapor deposited (CVD) nitride instead of sputtered nitride.

#### **EXPERIMENTAL RESULT**

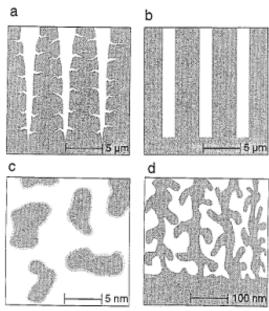

Ideally the pores should grow vertically into the bulk of the silicon starting from the surface. If the current densities are not maintained at the appropriate levels the pores might branch leading to an ill-defined final structure as seen in Figure-1. Also, higher applied voltages and currents can lead to considerable pore branching.

Fig-1: Effects of variations in etch parameters on pore geometry

There are two variations of this technique based on the nature of the pores and the usage of light during pore formation namely, macropores and nanopores (these are also called micropores in some literature, we refer to pores which has dimensions in nano scales as nano pores). In the macro porous etching, the pores are orderly and are initiated by KOH etch pits formed by lithography. Backside wafer illumination is also used to help the progression of etching in an anisotropic fashion. In the case of nano porous silicon light activation and pore initiation are not employed and the pores are random in nature with diameters in the nanometer range. We exploited the nano porous silicon formation in this research to achieve high aspect ratio structures, by dissolving these pores in standard silicon chemical etchants. The rate of porous silicon formation depends on a variety of factors such as HF concentration, applied current density, and dopant type/concentration Due to the dependence on holes for porous silicon formation, there exists a difference in the mechanism by which pores are formed in an N-type and a P-type substrate. P-type silicon which is rich in holes develops pores at any concentration, whereas N-type silicon in which holes are minority carriers requires some form of hole generation mechanism. Typically a light source is used to pump photons into the substrate for hole generation in N-type silicon for pore formation.

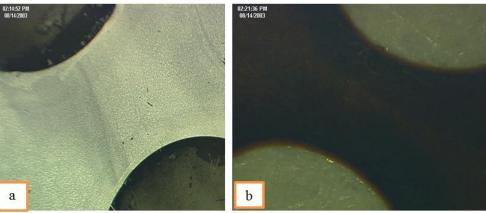

Fig-2(a): Micro photographs of circular shapes etched for porous silicon. (b) Substrate after pore dissolution

As seen from Figure-2, on the right the pattern has porous silicon in selective area. N-type silicon can be employed in a P-type substrate as an etch stop layer for pore formation and pore formation is significantly reduced while progressing from an N-type area to a Ptype region. To establish the feasibility of this research experiments were carried out to a) localize the porous silicon formation to only certain regions of the wafer b) achieve a highly anisotropic, minimally branched pore profile c) maintain the straightness of the overall structure walls. Traditional porous silicon processing involves forming pores throughout the surface of the wafer. Previous work has been reported in literature regarding localizing pores, but this is confined to shallow structures which are not very deep. We have successfully been able to localize pores only in the regions of interest and prevent pore formation in the rest of the wafer by using a combination of etch masks.

# **CONCLUSION**

We were able to fabricate nanopores selectively using a p type silicon wafer and the pattern was defined using silicon nitride as the masking layer and forming the least resistance path for the areas where nanopores are to be formed. Nanopores were formed and they were then etched using anisotropic etchant to etch away the nanopores silicon quickly at room temperature. This allows us to make optical quality surface useful for optical application. This process is not only cost effective but also provides a smoother surface which are the two major advantage of this process.

## **REFERENCES**

- 1. Lehmann, V. U. G. (1991). Porous silicon formation: A quantum wire effect. *Applied Physics Letters*, 58(8): 856-858.

- 2. Lehmann, V. (1997). The limits of macropore array fabrication. *Thin Solid Films*, 297: 13-17.

- 3. Charlton, M. H. L., & Parker, G. (1996). High aspect ratio photo-assisted electrochemical etching of silicon and its applications for the fabrication of

- quantum wires and photonic band structures. IEEE Colloquium on Micro engineering Applications in Optoelectronics, 1-5.

- Kedia, S., Samson, S., & Bach, L. (2015). Total internal reflection-based free space optical communication system. *Journal of Microelectromechanical Systems*, 24(5):1632-1641.

- 5. Steiner, W. L. (1995). Micromachining applications of porous silicon. *Thin Solid Films*, 255: 52-58.

- 6. Lehmann, V. (1993). The physics of macropore formation in Low Doped N-Type Silicon. *Journal of the Electrochemical Society*, 140: 2826-2843.

- 7. Steiner, W. L. (1995). Micromachining applications of porous silicon. Thin Solid Films, 255: 52-58.

- 8. Samson, S., Agarwal, R., Kedia, S., Wang, W., Onishi, S., & Bumgarner, J. (2005). Fabrication processes for packaged optical MEMS devices, 2005 International Conference on MEMS, NANO and Smart Systems, Banff, Alta., Canada, 113-118.

- 9. Ohji, P. J. T., & French, P. J. (1998). Fabrication of free standing structures using single step electrochemical etching in hydrofluoric Acid. Proceedings of the IEEE MEMS, Heidelberg, 246-250.

- Lehmann, V. (1996). Porous silicon A new material for MEMS. IEEE, 1-6.

- 11. Welty, R. J., Park, S. H., & Asbeck, P. M. (1998). Porous silicon technology for RF integrated circuit applications. IEEE, 160-163.

- 12. Lammel, G., & Renaud, P. H. (2000). Free-standing, mobile 3D porous silicon microstructures. Sensors and Actuators, 85; 356–360.

- Mescheder, U. M., Kovacs, A., Kronast, W., Barsony, I., Adam, M., & Ducso, C. (2001). Porous silicon as multifunctional material in MEMS Nanotechnology, 2001. IEEE-NANO 2001. Proceedings of the 2001 1st IEEE Conference on, 483-488.